| Enseignements en DEUG2 Informatique |

|

|

|

|

|

|

La Mémoire Cache

Définition

La mémoire cache (antémémoire) à pour but d'améliorer les performances de la mémoire traditionnelle (SDRAM, DDR-SDRAM, RDRAM). La mémoire, de par sa lenteur relative, n'est pas en mesure de délivrer les données aussi rapidement que le processeur est capable de les traiter.

Le principe de la mémoire cache est d'insérer entre le processeur et la mémoire traditionelle, une faible quantité de mémoire très rapide qui stocke les informations les plus récentes ou les plus souvents accédées.

On peut reprendre le même principe pour les disques durs et CD/DVD. Le temps d'accès de la mémoire et de l'ordre de la ns alors que celui du disque dur est de la ms. Les disques durs actuels contiennent une quantité de RAM qui joue le rôle de cache entre mémoire de la machine et le disque.

Caches de niveau 1, 2, 3

Entre processeur et mémoire il existe 3 niveaux de cache. Les caches se sont rapprochés progressivement du die du processeur à mesure que la finesse de gravure diminuait et permettait de placer plus de transistors sur le die. Initialement la mémoire cache se trouvait sur la carte mère.

- Cache de niveau 1 (Level 1)

Actuellement, le cache de niveau 1 se situe à l'intérieur du processeur, il est généralement constitué de deux parties, l'une stockant les instructions et l'autre les données. Sa taille varie de 16 à 128 ko

Pentium III

Pentium III

- Cache de niveau 2 (Level 2)

Le cache de niveau 2 possède une taille plus grande que le cache de niveau 1 (excepté sur les AMD Duron) et se situe actuellement sur le die du processeur. Auparavant il se situait au niveau de la carte mère. Sa taille varie de 64 à 512 ko.

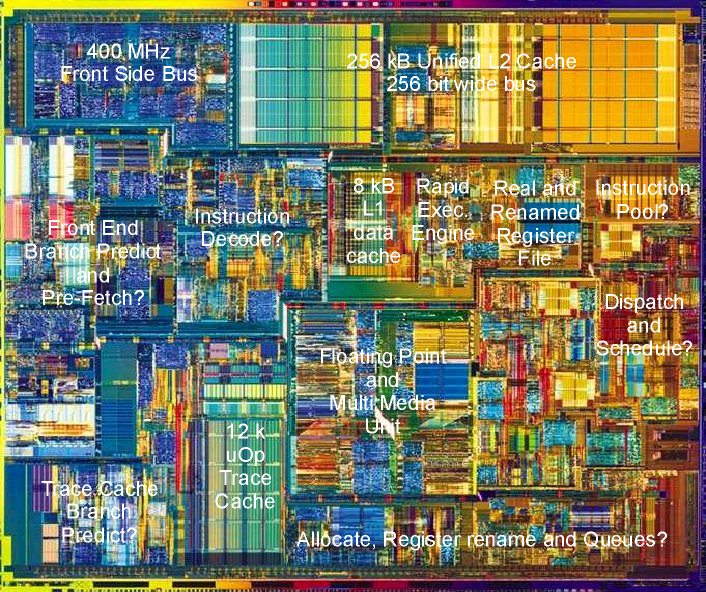

Pentium 4

Pentium 4

- Cache de niveau 3 : Level 3

Le cache de niveau 3 se situe au niveau du die également ou sur la carte mère. On le trouve surtout sur les machines haut de gamme (Sun, Hp Server, IBM...). Sa taille varie de 1 à 8 Mo.

-

Exemples de caches :

| Processeur | Cache L1 | Cache L2 | Vitesse | Cache L3 |

| Pentium II | 32 ko | 512 ko | 50 % | aucun |

| Pentium III (Katmai) | 32 ko | 512 ko | 50 % | aucun |

| Pentium III (Coppermine) | 32 ko | 256 ko | 100 % | aucun |

| Pentium 4 | 8 ko + 12 ko | 256 - 512 ko | 100 % | aucun |

| Pentium 4 (Extreme Edition) | 8 ko + 12 ko | 256 - 512 ko | 100 % | 1 à 2 Mo |

| Itanium | 32 ko | 96 ko | 100 % | 2 ou 4 Mo |

| AMD Duron | 64+64 ko | 64 ko | 100 % | aucun |

| AMD Athlon | 64+64 ko | 256 ko | 100 % | aucun |

| AMD Athlon XP | 64+64 ko | 512 ko | 100 % | aucun |

| AMD Athlon 64 | 64+64 ko | 1 Mo | 100 % | aucun |

Types de caches

Les caches ont pour but de stocker les données ou les instructions utilisées par le processeur. Les données et instructions sont identifiées par leur adresse, le cache peut être représenté sous forme d'une table qui stocke donc une adresse et la donnée présente à cette adresse.

Il existe 3 types de caches :

| Type de cache | Fonctionnement | Avantage | Inconvénient |

| à accès direct | une donnée sera toujours stockée au même emplacement dans la table en fonction de son adresse | rapidité d'accès | recouvrement des adresses appartenant à la même classe d'équivalence |

| associatif | une donnée peut être stockée dans n'importe quel emplacement de la table quelque soit son adresse | on peut stocker plusieurs adresses appartenant à la même classe d'équivalence | temps de recherche dans la table ou complexité du circuit effectuant la recherche en prarllèle |

| associatifs à n groupes | correspondent à une amélioration des caches à accès direct avec plusieurs sous-tables. Un cache associatif à 4 groupes permet de stocker 4 données dont les adresses appartiennent à la même classe d'équivalence |

|

aucun |

Composants des caches

Comme nous l'avons vu on utilise la mémoire statique plus rapide que la mémoire dynamique dans la conception des caches :- Mémoire Async SRAM :

Il s'agit d'une mémoire asynchrone offrant des temps d'accès de 12 à 20 ns. Elle est performante pour des fréquences de bus aux alentours de 33 Mhz.

- Mémoire Sync SRAM :

Il s'agit d'une mémoire synchrone de temps d'accès de 8 à 12 ns efficace pour les fréquences de bus ne dépassant pas 66 Mhz.

- Mémoire PBS RAM (Pipelined Synchronous Burst SRAM)

Elle s'adapte beaucoup mieux aux fréquences de bus élevées (133 Mhz) et son temps d'accès varie de 4 à 8 ns.

Utilité des mémoires caches

| Niveau d'accès |

Temps d'accès |

| Registre | 2 ns |

| Cache L1 | 4 ns |

| Cache L2 | >5 ns |

| Cache L3 | 30 ns |

| DRAM | 60 ns |

| Disque Dur | 12.000.000 ns |

L'obtention d'une donnée par le processeur consiste :

- premièrement à vérifier si l'adresse que l'on tente d'accéder est présente dans le cache L1, si c'est le cas la donnée associée est retournée au processeur,

- sinon on vérifie si l'adresse est présente dans le cache L2, si c'est le cas la donnée associée est retournée au processeur et est éventuellement copiée dans le cache L1 (cas d'un cache inclusif),

- si ce n'est pas le cas on accède à la mémoire et on recopie la donnée au niveau du cache L1 et/ou L2.

| Précédent | Sommaire | Suivant |